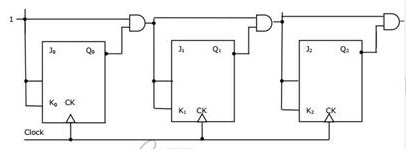

Find the maximum clock frequency at which the counter in the figure below can be operated. Assume that the propagation delay through each flip flop and each AND gate is 10 ns. Also assume that the setup time for the JK

inputs of the flip flops is negligible.

as described https://gateoverflow.in/26442/gate1991_5-c?show=151785#c151785

the answer is 50MHz ........my question is

Answer not should be 30(3 And Gate ) + 10 ( Synch Circuit) = 40 ns

1/40 ns= 25 Mhz ?

Why here they have taken it only for 1 And and 1 FF ?

Note;I will close it when get satisfactory answer.