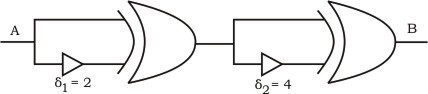

Consider the following circuit composed of XOR gates and non-inverting buffers.

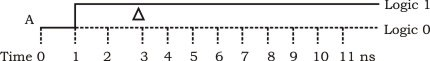

The non-inverting buffers have delays $\delta_1 = 2 ns$ and $\delta_2 = 4 ns$ as shown in the figure. Both XOR gates and all wires have zero delays. Assume that all gate inputs, outputs, and wires are stable at logic level $0$ at time $0$. If the following waveform is applied at input $A$, how many transition(s) (change of logic levels) occur(s) at $B$ during the interval from $0$ to $10$ ns?

- $1$

- $2$

- $3$

- $4$