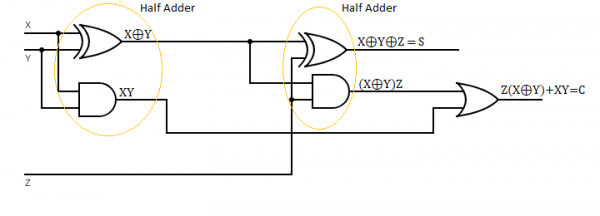

Circuit diagram for the problem can be made as:

delay for XOR gate = 2*1.2 = 2.4 μs.

delay for AND/OR gate = 1.2 μs.

First XOR gate takes 2.4 μs. and meanwhile XY can be calculated in parallel. Similarly, Second XOR gate takes another 2.4 μs and in the meanwhile output of AND(1.2 μs) and OR(1.2 μs) can be calculated (Since, the output of first XOR and AND is available immediately).

So, total time taken = 2.4 + 2.4 = 4.8 μs for 1-bit calculation.

Hence, gate delay for 4-bits = $4*4.8=19.2\ μs$.