In addition to the Best answer for this question , i am adding diagramatical representation for Ripple carry Adder for ease of understanding.

We know that:

Gi=AiBi,

Pi=Ai⊕Bi and

Si=Pi⊕Ci

Also

C1=G0+P0C0

C2=G1+P1G0+P1P0C0

C3=G2+P2G1+P2P1G0+P2P1P0C0

C4=G3+P3G2+P3P2G1+P3P2P1G0+P3P2P1P0C0

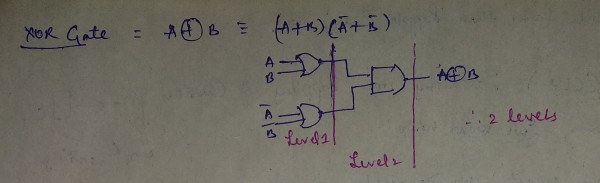

XOR can be implemented in 2 levels; level-1 ANDs and Level-2 OR.

Fig 1:

Hence it would take 2 time units to calculate Pi and Si

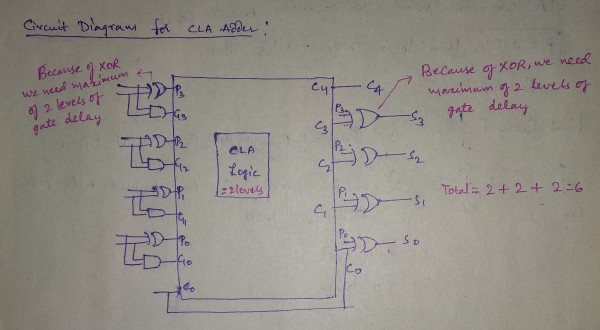

The 4-bit addition will be calculated in 3 stages:

Fig 2:

1. (2 time units) In 2 time units we can compute Gi and Pi in parallel. 2 time units for Pi since its an XOR operation and 1 time unit for Gi since its an AND operation.(Refer Fig 2)

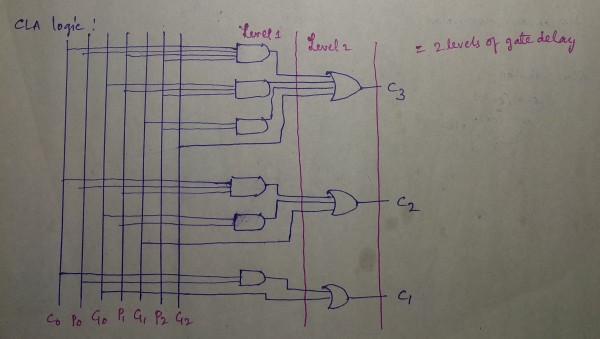

2. (2 time units) Once Gi and Pi are available, we can calculate the caries, Ci, in 2 time units.(Refer Fig 3)

Fig 3:

Level-1 we compute all the conjunctions (AND). Example P3G2,P3P2G1,P3P2P1G0P3G2,P3P2G1,P3P2P1G0 and P3P2P1P0C0P3P2P1P0C0 which are required for C4.

Level-2 we get the carries by computing the disjunction (OR).

3. (2 time units) Finally we compute the Sum in 2 time units, as its an XOR operation.(Refer Fig 2)

Hence, the total propagation delay is 2 + 2 + 2 = 6 time units.