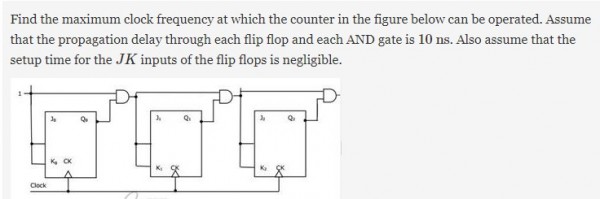

Consider the following question:

My explanation:

A clock cycle time should be large enough that all flip-flops can come in a stable state before the next clock cycle starts.

Suppose cycle 1 is just completed and cycle 2 is just about to start:

1. to reach the result of q0Λ1 to J1K1 it needs $10 ns$

2. to reach the result of (q0Λ1)ΛQ1 to J2K2, 10 more nanoseconds are needed.

3. Now, we need 10 more nanoseconds to operate flipflops as the propagation delay of each flip flop is 10ns.

Answer should be (1/(2*10ns + 10ns) = $\frac{1}{30ns}$.

But in the answer given by Arjun on the following link, it is $\frac{1}{20ns}$. Can someone explain, please?

https://gateoverflow.in/26442/gate1991_5-c