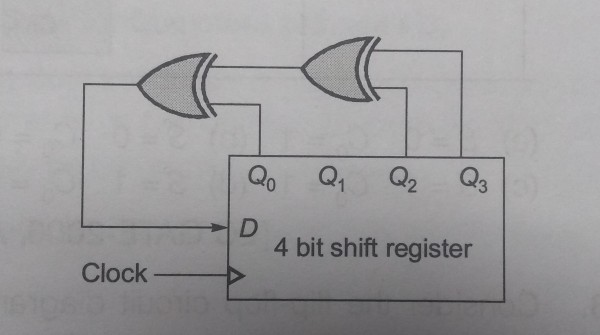

A 4 bit right shift register is shifting the data to the right for every clock pulse. The serial input D is derived by using XOR gates as shown. After 3 clock pulses the content in the register is to be 1010 at Q0Q1Q2Q3. What were the initial contents of the register?

- 1100

- 1010

- 0011

- 0101

I’m getting the answer as 0101 but it’s given 0011