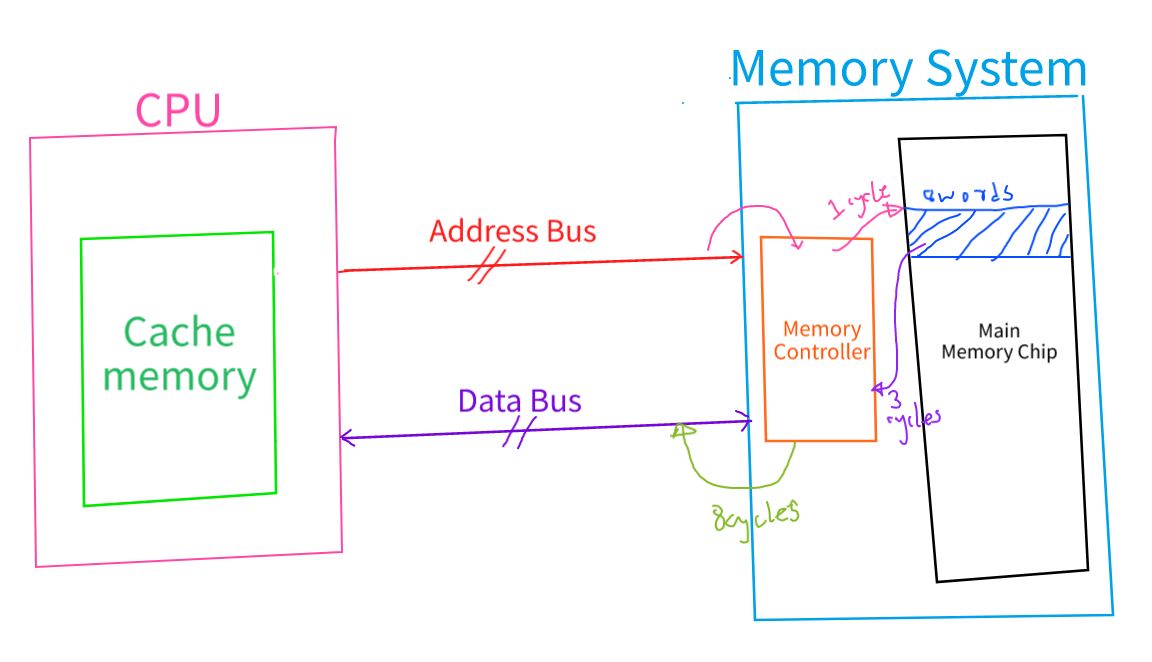

Few things which are to be noted here are as follows. The memory controller is a part of the “memory system”. The memory system quite obviously also has the memory chip where the data are actually stored. Now the question asks to find the maximum bandwidth of the “memory system”. Now bandwidth of the memory system is the data transfer speed of the memory system, i.e. considering memory system as a black box, how much data can be retrieved from it per unit time.

Now as per the question it takes $1$ cycle to select the first address of the block by the memory controller.

It takes $3$ cycles to read $8$ words from the memory chip to the memory controller. [Note that the memory controller is a part of the memory system, so $8/3$ words/cycle is not the required bandwidth, we need to find data rate for data entering or leaving the memory system!!]

Lastly it takes $8$ cycles to transfer the $8$ words to the data bus.

So in a period of $1+3+8(=12)$ cycles, $8$ words or $32$ bytes of data are retrieved from the memory system. So in a system which issues a series of read request, the maximum bandwidth of the memory system shall occur when there is a miss!! [Had there been no miss, the memory system shall be idle and bandwidth shall be $0$ in that case.] So in a system issuing a series of read requests, in $12$ cycles or $12*\frac{1}{60 *10^6}$ secs we can get max of $32$ bytes of data out of the memory system.

So required bandwidth = $\frac{32}{12*\frac{1}{60 *10^6}}$ bytes/sec = $160 * 10^6$ bytes/sec