" a cross-coupled R-S flip-flop realized with two NAND gates may lead to an oscillation "

Oscillation means output is going to change every time.

As, 2 NAND gates are there , other 2 might be AND gate.

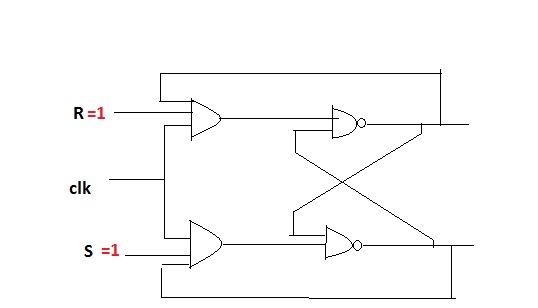

Now, circuit diagram will be like this

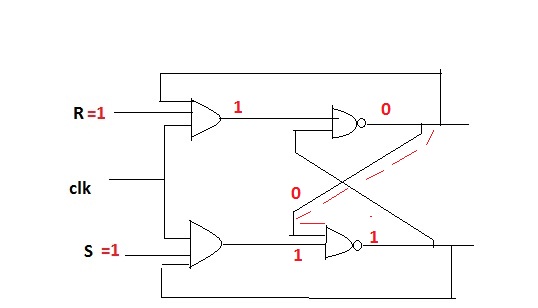

A) Now, at first R is getting 1 , that corresponding NAND gate producing 0.

That 0 is input of another NAND gate,

So, NAND gate corresponding to S getting input as 1 NAND 0=1 (As shown in picture below)

Now, it's 1st output is 0 1

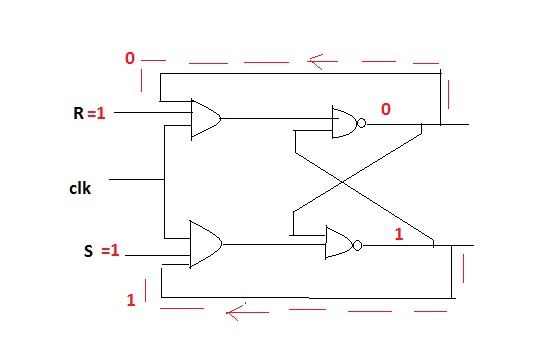

Next, 0 1 ouput is giving input to R and S

So, AND gate of R is producing 0 AND 1=0

NAND gate of R is giving 0 NAND 1=1(See picture again)

Similarly , AND gate of S getting input 1AND 1=1

R value previously was 0 (We donot know, R will produce first or S will produce first, So, taking previous value of R)

for NAND gate it is getting 0 NAND 1=1

So, 2nd output here is 1 1

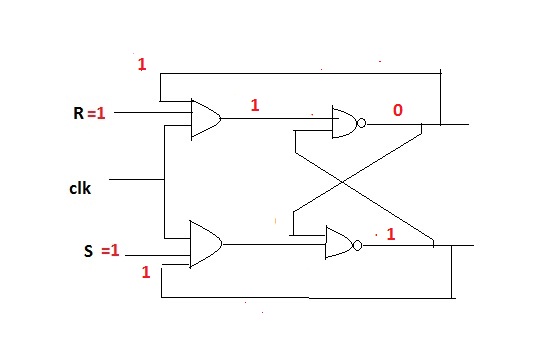

Similarly keep check 1 1 as input as next AND gates

it will produce 0 0

So, if we put 11 as first input, it will keep toggleing , producing 01--11--00--11--00-------------------

D) if we give 00 first in same circuit it will produce as output 00--11--11--11--11------------------

So, output will not toggle ,after reaching 11 state.

B) if we give 01 as input it will produce 10--11--10--11----------------

means only S (or we can say any one output) will toggle , but not both.

C)Similar reason as B)