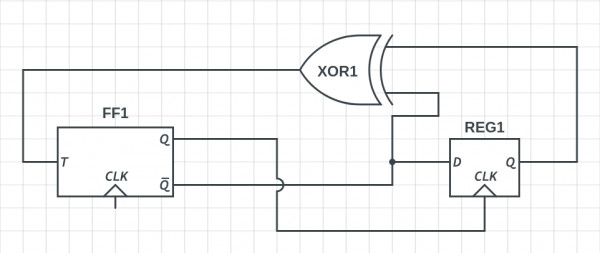

Flip flops are positive edge triggered.

T = Q1’ ⊕ Q0

D = Q1’

| Q0 |

Q1 |

Q0 (Next) |

Q1 (Next) |

D |

T |

| 0 |

0 |

1 |

1 |

1 |

1 |

| 1 |

1 |

1 |

0 |

0 |

1 |

| 1 |

0 |

1 |

0 |

1 |

0 |

| 1 |

0 |

1 |

0 |

1 |

0 |

At Time 0: Initial state (Q0 Q1) = (0, 0)

At Time 1: Since T is 1 i.e. trigger so Q1 will change its state to 0 → 1 now this change of state is given as CLK to D FF and that is +ve edge triggered so Q0 will also change its state from 0 → 1 because i/p to D FF is 1. Therefore (Q0, Q1) = (1, 1)

At time 2: Here T is 1, so state of Q1 is changed from 1 → 0 but this will act as -ve edge to D FF so Q0 will not change its state. Therefore (Q0 Q1) = (1,0)

At time 3: i/p to T FF is 0 i.e. latch so Q1 will retain its state 0 → 0, this will act as -ve level to D FF so Q0 will not change its state. Therefore (Q0 Q1) = (1,0)

Now it will stuck at (1,0)

Therefore: 00 → 11 → 10 → 10 is correct answer.