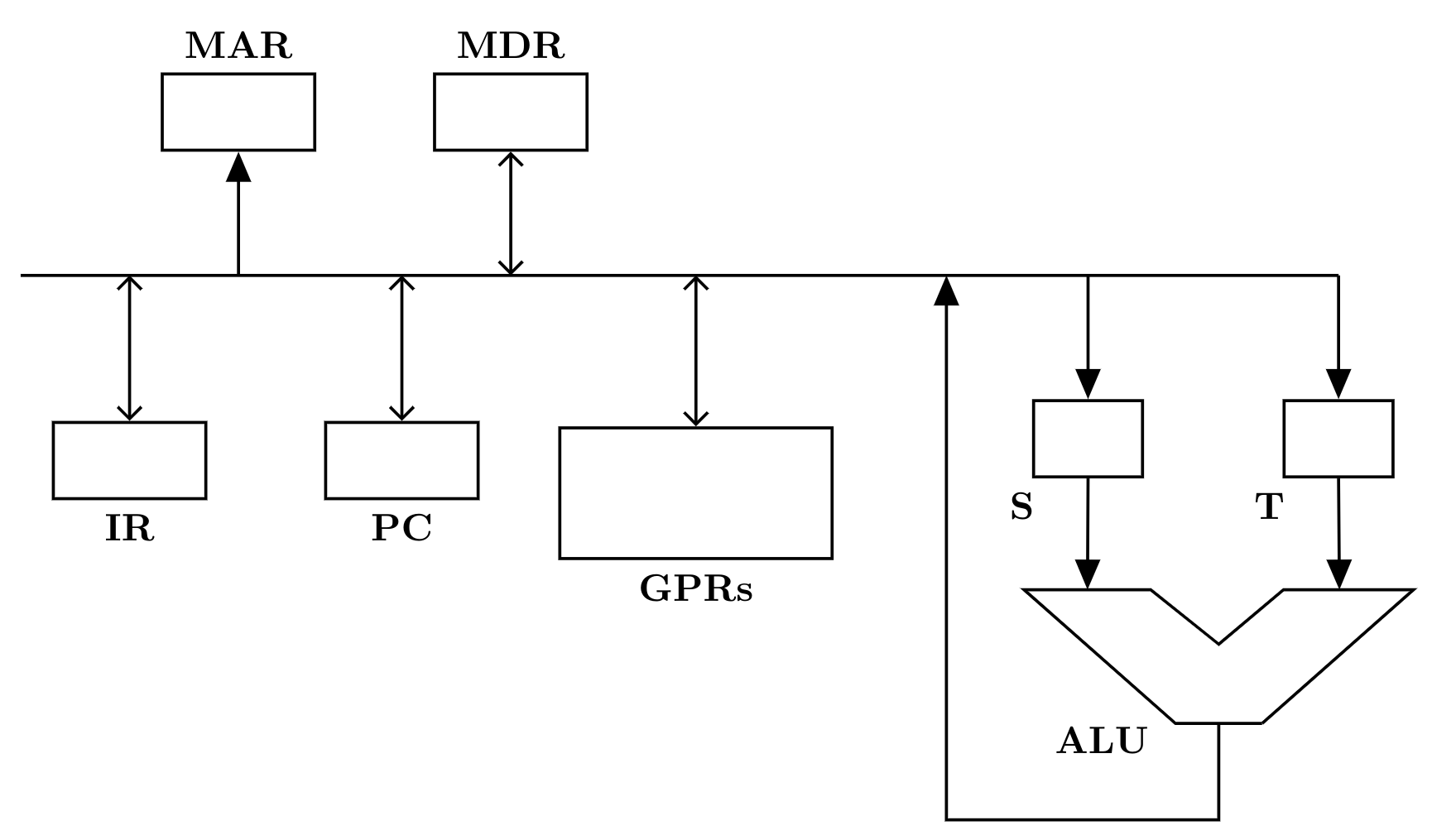

Consider the following data path of a $\text{CPU}.$

The $\text{ALU},$ the bus and all the registers in the data path are of identical size. All operations including incrementation of the $\text{PC}$ and the $\text{GPRs}$ are to be carried out in the $\text{ALU}.$ Two clock cycles are needed for memory read operation – the first one for loading address in the $\text{MAR}$ and the next one for loading data from the memory bus into the $\text{MDR}.$

The instruction "call Rn, sub” is a two word instruction. Assuming that $\text{PC}$ is incremented during the fetch cycle of the first word of the instruction, its register transfer interpretation is

$\text{Rn} \leftarrow \text{PC} + 1$;

$\text{PC} \leftarrow \text{M[PC]}$;

The minimum number of CPU clock cycles needed during the execution cycle of this instruction is:

- $2$

- $3$

- $4$

- $5$