i have tried best possible solution...

consider below diagram in which 'A' represents ;Akriti' & 'B' represnts 'Basmati'your friend

now akriti wants to meet her friend basmati who lives at certain distance (as mentioned in figure by a line)

now the time taken by akriti to reach basmati (consider 1 minute) is called propgation delay.

now consider below figure in which A as akriti and A1 as akriti1 lives at same place so is case with B basmati & B1 as basmati1

now assume both akriti & akriti1 want to meet respective basmati's so they leave at same time and travel same distance...so the time taken by both will be 1 minute .

how 1minute ..see individually they have travelled 1-1 minute respectively but we cannot take 2minutes as propogation delay...assume both left at 10:15 am and they reached at 10:16 so only 1 minute propogation delay...in that 1 minute either 1 akriti travels or 100 akriti travels delay will be only 1 minute not 100 minutes ...same concept is used in question

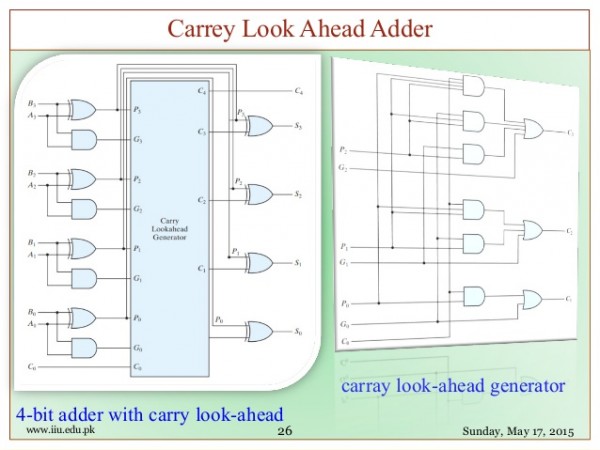

now consider our question i m considering 1 of the way to draw look ahead carry adder there may be other ways also but the carry generator is same as given in the question i.e is 2- level AND-OR

there r 2 figures in above picture the right hand part called as look ahead carry generator is part of left hand figure that have to put inside blue box given///for clearer view i considered this picture.

now consider RHS part( generator's part) assume

if we give input to AND gate it gives output after 1 minute as there were 2 akriti's here 6 AND gates

i.e AND1,...AND6..so it will take only 1 minute to give output by all AND gates...( not 6 minutes )

and after that output is fed as a input to OR gate which again takes 1 minute to give output...same as AND gate ...to total 2 minutes time taken by the carry generator..

now take LHS figure in which 2 more levels are there...in first level

ex-0r & AND gates ,i.e x-0r1 & AND1.....ex-0r4 & AND4..will again take only 1minute to give output

and in last level ex-or gate same concept....... again will take 1 minute to give output ....so if we add all we get total 4 minutes of delay ....i.e 1min by first level ////2min by carry generator///1 min by last level