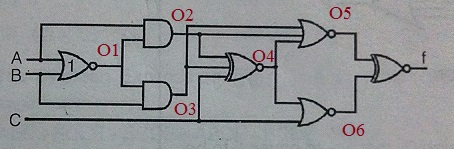

I have marked output from various gates as O1, O2, O3, O4 , O5 and O6

Now f = O5 EXOR O6

O1 = A NOR B = (A+B)' = A'B'

O2 = O1 AND A = (A'B').A = 0

O3 = O1 AND B = (A'B').B = 0

O4 = O2 XNOR O3 XNOR C = 0 XNOR 0 XNOR C = 1 XNOR C = C

O5 = (O2+O3+O4)' = (0+0+C)' = C'

O6 = O4 NOR C = (C+C)' = C'

f = O5 EXOR O6 = C' XNOR C' = C' + C = 1

So Answer can be both B) and D)