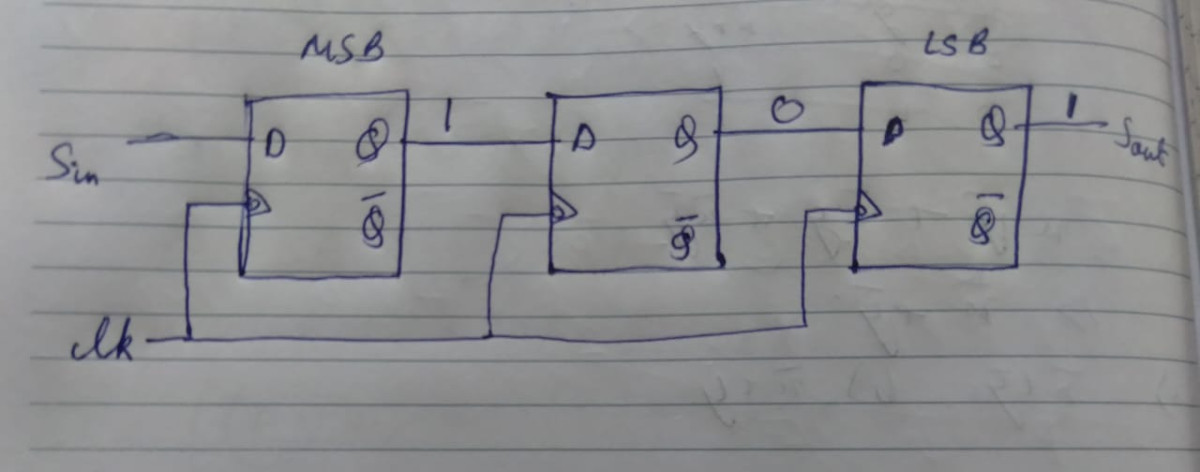

For a 3 bit Shift Register SISO, you have stored 101 which took 3 clock pulses. Now the register looks something like this.

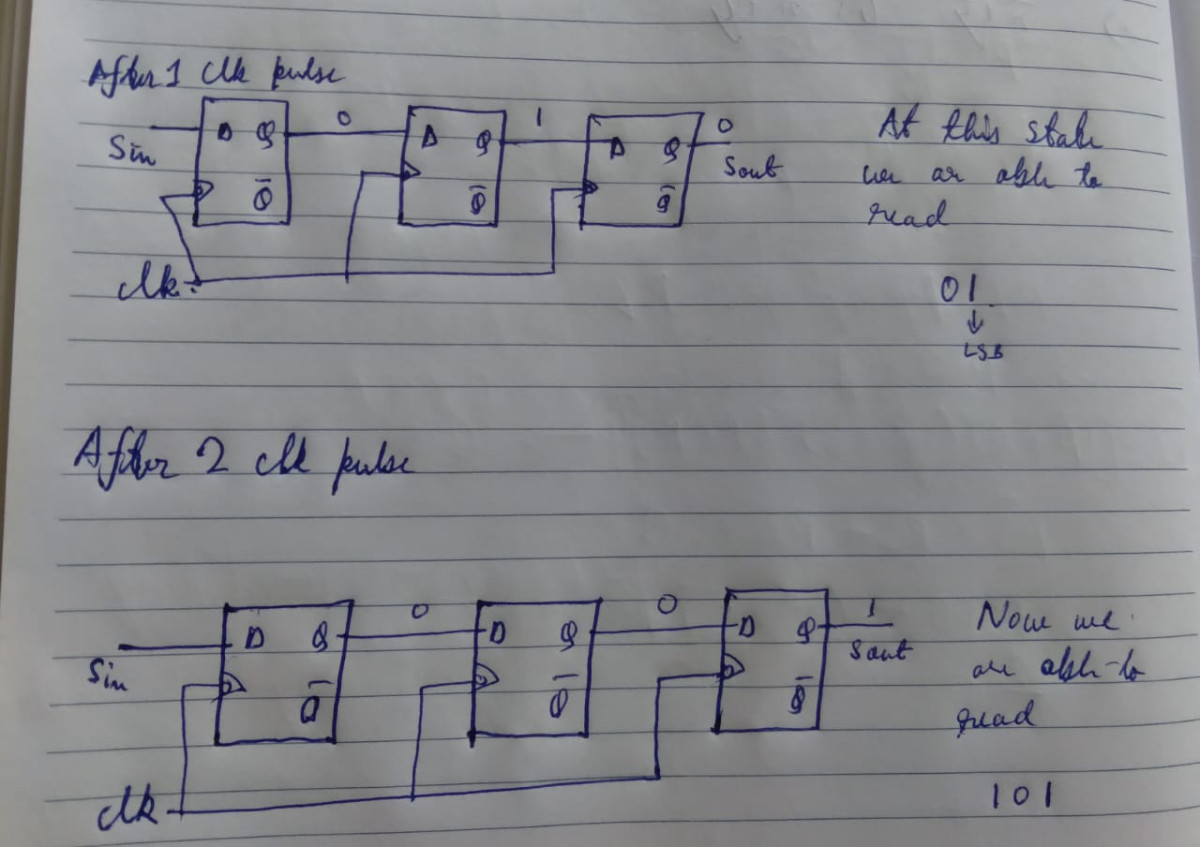

Now to read the 101 it will only take 2 clock pluse, because at this moment we are able to read the least significant bit 1(which is present in Sout). The following will we the condition after each clock pulse. (Note : in order to read the bit we will input 0 from Sin)

To Generalize : Since after storing the bits in a n-bit Shift Register with Serial Out, we always have a bit which is present in Sout, we are able to read. Thus, we only need n-1 clock pulses to read the complete stored bit.