I tried the following way ...

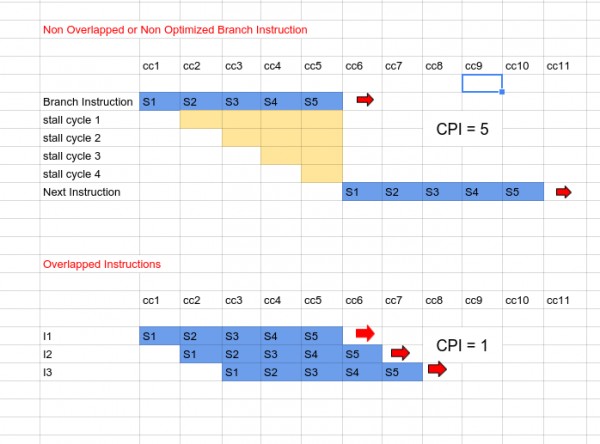

For each of 20% of the NON OVERLAPPED instructions we are getting 4 stall cycles and therefore CPI for these instruction is 5

For other 80% of the OVERLAPPED instructions we are not getting any stalls and pipeline will output one instruction per cycle. There for in this case CPI = 1

Average CPI = $0.2*5 \ + \ 0.8*1 = 1.8$

So Throughput in MIPS = $\frac{1}{1.8*10*10^{-9}} \ * \frac{1}{10^{6}} = 55.55$