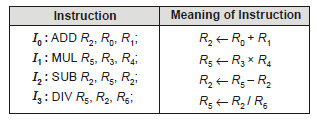

A 5 stage pipelined processor has instruction fetch (IF), operand fetch (OF). Instruction decode (ID), perform operation (PO) and Write operand (WO) stages. The IF, ID, OF and WO stages takes 1 clock cycle each for any instruction. The PO stage takes 1 clock cycle for ADD and SUB instruction, 2 clock cycles for MUL instruction and 4 clock cycles for DIV instructions respectively. The number of clock cycles needed to execute the following sequence of instruction where operand forwarding from WO to PO and PO to OF is used